- Technology

- PCI Express

PCI Express and AMD Technology

High performance, low power Integrated Blocks for PCI Express

- Overview

- Versal Solutions

- UltraScale+ Solutions

- UltraScale Solutions

- 7 Series Solutions

- Documentation

Overview

PCI Express® (PCIe®) is a general-purpose serial interconnect suitable for a broad range of applications across communications, data center, enterprise, embedded, test & measurement, military, and other markets. It can be used as a peripheral device interconnect, a chip-to-chip interface, and as a bridge to many other protocol standards.

AMD provides high-performance, low-power integrated blocks for PCI Express as a hardened sub-system in many devices.

AMD also provides PCIe DMA and PCIe bridge hard and soft IP blocks that utilize the integrated block for PCI Express, boards with PCI Express connectors, connectivity kits, reference designs, drivers, and tools to make it easy to implement PCIe-based designs.

Select a device family from below to review the AMD PCIe solution portfolio for that family.

Versal Solutions

Systems leveraging implementations of the PCI Express® specification are pervasive in data center, communications, and embedded applications. The multiple connectivity options available in the Versal™ architecture directly support users’ needs to focus on their core competency while leveraging advanced standards-based interfaces. The integrated blocks for PCI Express in the Versal architecture offer premium performance levels with ease of use and efficiency over fully soft IP solutions. The Versal architecture integrates five types of integrated blocks for PCI Express:

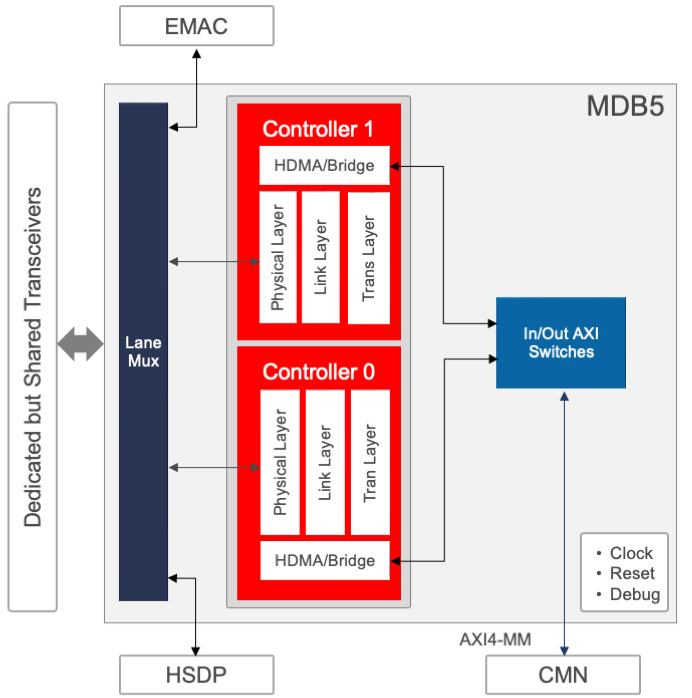

- MDB5: integrated block for PCI Express Rev. 5.0 with DMA/bridge

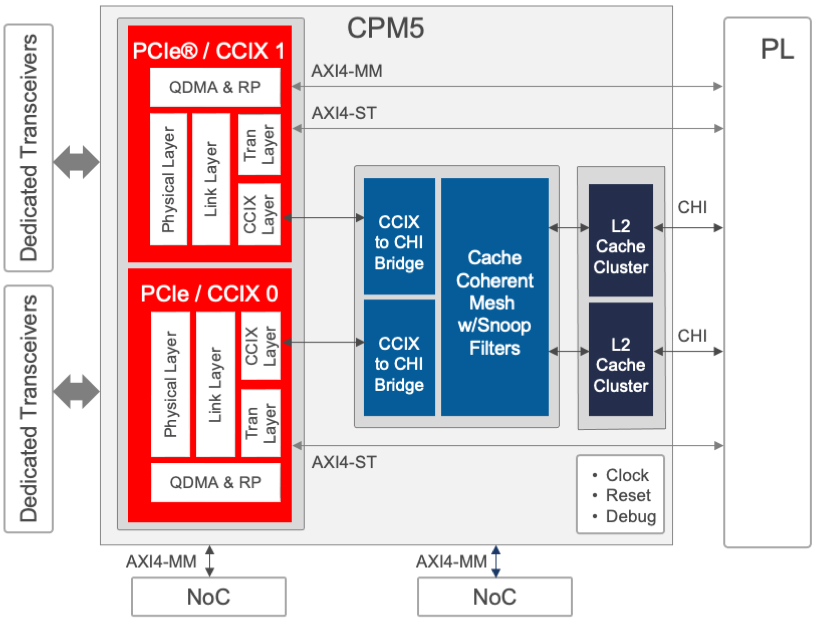

- CPM5: integrated block for PCI Express Rev. 5.0 with DMA/bridge

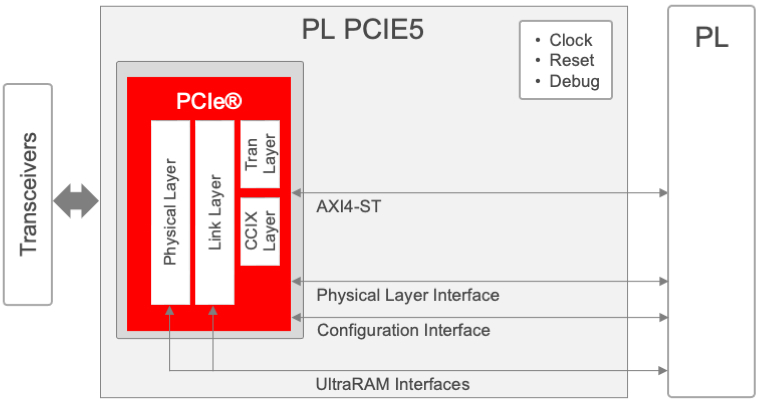

- PL PCIE5: integrated block for PCI Express Rev. 5.0

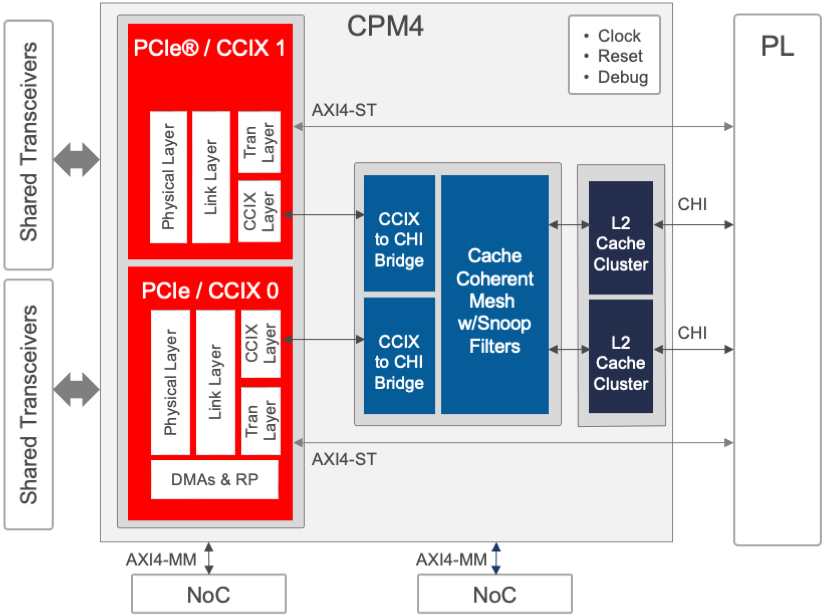

- CPM4: integrated block for PCI Express Rev. 4.0 with DMA/bridge

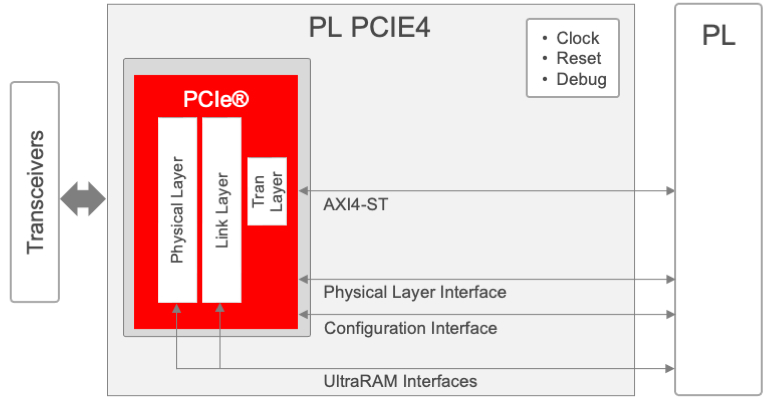

- PL PCIE4: integrated block for PCI Express Rev. 4.0

MDB5, CPM5, PL PCIE5, CPM4, and PL PCIE4, in conjunction with available GTYP and GTY transceivers, enable interface operation at specification-defined data rates. These range from 2.5 GT/s per lane with one lane (Gen1x1) up to their rated maximum link configurations, with some integrated blocks reaching 32 GT/s per lane with 8 lanes (Gen5x8) and 16 GT/s per lane with 16 lanes (Gen4x16).

The table below is a summary of key characteristics of the integrated blocks for PCI Express in the Versal architecture. Refer to the Versal Architecture and Product Data Sheet: Overview (DS950) for additional information on available resources and capabilities based on orderable device, package, and speed grade combinations.

Versal Architecture Integrated Blocks for PCI Express |

|||||

|---|---|---|---|---|---|

MDB5 |

CPM5 |

PL PCIE5 |

CPM4 |

PL PCIE4 |

|

| Associated Specifications |

PCIe Rev. 5.0 | PCIe Rev. 5.0 | PCIe Rev. 5.0 |

PCIe Rev. 4.0 |

PCIe Rev. 4.0 |

| Max PCIe Link Configs |

Gen5x4 2 x Gen5x2 Gen5x2 |

2 x Gen5x8 Gen4x16 2 x Gen4x 8 |

Gen5x4 Gen4x8 Gen3x16 |

Gen4x16 2 x Gen4x8 |

Gen4x8 Gen3x16 |

| PCIe Port Type Support |

EP, RP | EP, RP, Switch |

EP, RP, Switch |

EP, RP, Switch |

EP, RP, Switch |

| Key PCIe Features |

SR-IOV 8PF / 64VF |

SR-IOV 16PF / 4KVF |

SR-IOV 8PF / 4KVF |

SR-IOV 4PF / 252VF |

SR-IOV 4PF / 252VF |

| Integrated DMA/Bridge | Two Bridges, Required Choice of One or Two: Optional HDMA | Choice of One or Two:Optional QDMA/Bridge | - | Choice of One: Optional QDMA/Bridge Optional XDMA/Bridge |

- |

MDB5, CPM5, PL PCIE5, CPM4, and PL PCIE4 can be used at reduced link configurations to optimize product designs for cost, support novel form factors, alleviate board complexity, and shrink power budgets. Additionally, reduced link configurations can support lower programmable logic resource utilization, depending on the nature of any soft IP solutions used to expand the application-level capabilities of these integrated blocks. CPM5, PL PCIE5, CPM4, and PL PCIE4 can be configured as Endpoint (EP), Root Port (RP), and switch port types. See the Versal Adaptive SoC Integrated Block for PCI Express Product Guide (PG343) and Versal Adaptive SoC CPM Mode for PCI Express Product Guide (PG346). MDB5 can be configured as Endpoint (EP) and Root Port (RP) port types and must be used with its integrated DMA/bridge solution.

AMD enables users to focus design investment in their areas of greatest value by delivering pre-verified high-performance DMA/bridge subsystems for the integrated blocks for PCI Express in the Versal architecture. Available DMA/bridge subsystem options include:

- MDB5 contains two controllers for PCI Express and integrates two instances of an HDMA/bridge subsystem. Use of the integrated DMA is optional, and each instance is independently customizable. The HDMA subsystems provide a tight coupling to integrated processors and the AXI interconnect. The subsystems also include bridge functionality. Data can be moved with memory-mapped techniques, including the programmable network on chip (NoC).

- CPM5 contains two controllers for PCI Express and also integrates two instances of a QDMA/bridge subsystem. Use of the integrated DMA is optional, and each instance is independently customizable. The QDMA subsystems provide scalable queue-based DMA for moving enormous volumes of data with low latency, plus support for multiple physical and virtual functions commonly required by enterprise class products. Data can be moved with memory-mapped techniques, including the programmable network on chip (NoC), or with streaming techniques, into the Versal adaptive SoC’s programmable logic. The subsystems also include bridge functionality to the AXI interconnect.

- CPM4 contains two controllers for PCI Express and also integrates one instance of a QDMA/XDMA/bridge subsystem. Use of the integrated DMA is optional, and when used, can be configured as a QDMA subsystem like that in the CPM5 or as an XDMA subsystem. Data can be moved with memory-mapped techniques, including the programmable NoC, or with streaming techniques, into the Versal adaptive SoC’s programmable logic. The subsystem also includes bridge functionality to the AXI interconnect.

- PL PCIE5 and PL PCIE4 are individual controllers for PCI Express and are supported by soft IP implementations of DMA/bridge subsystems available at no cost through the Vivado™ Design Suite IP catalog.

For most users, the available DMA/bridge subsystems can provide time-saving infrastructures, enabling high-performance turnkey data movement. See the Versal Adaptive SoC DMA and Bridge Subsystem for PCI Express Product Guide (PG344) and Versal Adaptive SoC CPM DMA and Bridge Mode for PCI Express Product Guide (PG347). For users seeking to attach their own DMA/bridge subsystem—for preserving their driver and application software investment or to customize or optimize functionality using intimate knowledge of the end application—options are available to bypass the DMA/bridge of the CPM5 and CPM4. For ultimate freedom to implement fully custom solutions, AMD also provides a soft IP core PHY for PCI Express through the Vivado Design Suite IP catalog, enabling designers to attach their own controllers for PCI Express to available GTYP and GTY transceivers.

Supporting Products and Technologies

High-speed Serial Transceivers for PCI Express

Evaluation Kits by AMD for PCI Express

- Versal Prime Series VMK180 Evaluation Kit

- Versal AI Core Series VCK190 Evaluation Kit

- Versal AI Edge Series VEK280 Evaluation Kit

- Versal Premium Series VPK120 Evaluation Kit

- Versal Premium Series VPK180 Evaluation Kit

- Versal HBM Series VHK158 Evaluation Kit

UltraScale+ Solutions

AMD 16 nm UltraScale+™ devices integrate many essential PCI Express® features required for today’s data center, communications, and embedded applications. UltraScale+ devices use three types of integrated blocks: PCIE4, PCIE4C, and PCIE4CE.

The PCIE4 blocks are compliant to PCI Express Base Specification v3.1 and support up to Gen3x16 and can also be configured for lower link width and speeds. The PCIE4 block does not support Gen4 operation.

PCIE4C blocks are compliant to the PCI Express Base Specification v3.1, supporting up to 8.0 GT/s (Gen3) and compatible with PCI Express Base Specification v4.0, supporting up to 16.0 GT/s (Gen4). PCIE4C blocks are also compliant with CCIX Base Specification v1.0 Version 0.9, supporting speeds up to 16.0 GT/s. PCIE4C blocks support up to 16 lanes at Gen3 or up to 8 lanes at Gen4 and can be configured for lower link widths and speeds to conserve resources and power.

PCIE4CE blocks are compliant to the PCI Express Base Specification v4.0 supporting up to 16.0 GT/s (Gen4). PCIE4CE blocks support up to 16 lanes at Gen3 or up to 8 lanes at Gen4 and can be configured for lower link widths and speeds to conserve resources and power. Some devices contain only one revision of integrated block, whereas other devices provide a mix of revisions of integrated blocks.

All integrated blocks for PCIe® in the UltraScale™ architecture can be configured as Endpoint or Root Port. The Root Port can be used to build the basis for a Root Complex to allow custom chip-to-chip communication via the PCI Express protocol and to attach ASSP Endpoint devices, such as Ethernet controllers, Fibre Channel HBAs, or NVMe SSDs, to the FPGA, MPSoC, or RFSoC.

The Integrated Block for PCI Express IP is hardened in silicon and supports:

- Capability up to Gen3x16 in all revisions of integrated blocks, plus compatibility with Gen4x8 in devices offering PCIE4C blocks, plus compliance with Gen4x8 in devices offering PCIE4CE blocks. For specific link widths and rates that are supported, consult the IP product guide for the desired IP (PG213, PG195, or PG302). For details about PCIE4C block compatibility with Gen4x8, see PG213. Available link widths can depend on available transceiver counts and package pinout.

- Four physical functions and 252 virtual functions in support of single root I/O virtualization (SR-IOV) to share I/O resources.

- Expanded number of tags (256) to support more requests, enabling improvements in overall system performance.

- Integrated MSI-X tables.

AMD also offers high-performance DMA and bridge solutions as soft IP:

- The AMD QDMA IP sub-system is our leading DMA solution for PCIe. The QDMA provides support for SR-IOV with multiple physical and virtual functions with scalable queues. The QDMA also provides AXI bridge functionality. See Product Guide PG302 for more details.

- The AMD XDMA IP sub-system is our legacy DMA solution for PCIe, widely used by customers. The XDMA also provides AXI bridge functionality. See Product Guide PG195 for further details.

For ultimate freedom to implement fully custom solutions, AMD also provides a soft IP core PHY for PCI Express, enabling designers to attach their own controllers for PCI Express to available transceivers.

Supporting Products and Technologies

High-speed Serial Transceivers for PCI Express

Evaluation Kits by AMD for PCI Express

UltraScale Solutions

AMD 20 nm UltraScale™ devices integrate many essential PCI Express® features required for today’s data center, communications, and embedded applications.

The Integrated Block for PCI Express IP is hardened in silicon and supports:

- Native Gen3x8* Integrated PCIe® block

- 64 tags for PCIe requests

- Multi-vector MSI for up to 32 vectors and MSI-X

- See Product Guide PG156 for further details

AMD also offers high-performance DMA and bridge solutions as soft IP:

- The AMD XDMA IP sub-system is our production PCIe DMA solution, widely used by customers. See Product Guide PG195 for more information.

- AMD provides a production AXI Memory Mapped to PCI Express Bridge IP. See Product Guide PG194 for further details.

*For specific link widths and speeds that are supported, see the appropriate product guide for the desired IP (PG156, PG195, or PG194).

Supporting Products and Technologies

High-speed Serial Transceivers for PCI Express

7 Series Solutions

AMD 28 nm 7 series devices integrate many essential PCI Express® features required for today’s data center, communications, and embedded applications.

The Integrated Block for PCI Express IP is hardened in silicon and supports:

- Native Gen3x8* Integrated PCIe® block

- 64-bit and 128-bit data widths

- See Product Guide PG054 for further details

AMD also offers high-performance DMA and bridge solutions as soft IP:

- The AMD XDMA IP sub-system is our production PCIe DMA solution, widely used by customers. See Product Guide PG195 for more information.

- AMD provides a production AXI Memory Mapped to PCI Express Gen2 IP. See Product Guide PG055 for further details.

*For specific link widths and speeds that are supported, see the appropriate product guide for the desired IP (PG054, PG055, or PG195).