# **AUPERA: SMART WORLD VIDEO AI ANALYTICS**

### INTRODUCTION

Many aspects of life are utilizing video analytics to solve real problems and make business and people's lives smarter, whether this is smart City applications that monitor traffic congestion, parking lot availability and detect crime, to monitoring COVID-19 requirements for face masks and social distancing, to a smart building where secure points can be controlled via facial recognition for far better security than a badge. However, these applications are complex and require deterministic low latency, requiring an architecture that can deliver performance while maintaining an advantageous tCo.

Aupera's smart World solution, built on AMD Alveo $^{\text{\tiny{M}}}$  accelerator cards, Versal $^{\text{\tiny{M}}}$  ACAP, and Zynq $^{\text{\tiny{M}}}$  soCs, delivers high throughput, low latency with unsurpassed performance at a low hardware investment, assuring best-in- class tCo.

Built on the integration of the AMD Video Machine learning streaming server (VMss) framework with Aupera's AupXstream video analytics pipeline processing, these solutions enables hassle free field deployment even with custom models.

## **SOLUTION OVERVIEW**

Aupera smart World video Ai solutions support very high density of video feeds from multiple full HD cameras for object identification and classification. The additional unique proposition of this solution is its ability to run multiple inferencing models concurrently and deliver accurate results at a deterministic low latency, resulting in industry-leading low total Cost of ownership (tCo).

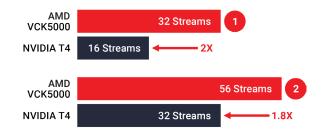

## THROUGHPUT ADVANTAGE

## **TCO ADVANTAGE**

1. AI MODEL: YOLOV3+: RESNET 18 HW: 1X AMD VCK5000 VS 1 X NVIDIA T4

2. AI MODEL: RESNET 50 & TINYYOLOV3

## **FEATURES AND BENEFITS**

## **Full FPGA Accelerated Pipeline**

- > Real-time, low-latency, high throughput

- > Concurrent multi-model inference

- > Best-in-class accuracy

### **Best-in-Class TCO**

- > Fewer servers and lower power

- > Fast deploying, turnkey solution

## Adaptable & Extensible Framework

- > Ready for edge, datacenter, and cloud deployment

- > Support for 3rd party plugins

- > Standard APi interface

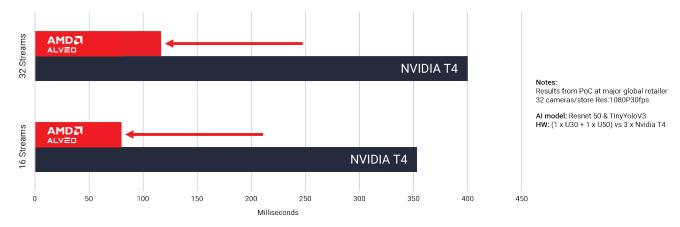

NOTES: RESULTS FROM POC AT MAJOR GLOBAL RETAILER 32 CAMERAS/STORE RES:1080P30FPS AI MODEL: RESNET 50 & TINYYOLOV3 HW: (1 X U30 + 1 X U50LV) VS 3 X NVIDIA T4

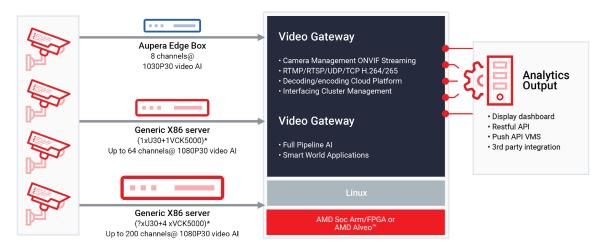

### **SOLUTION DEPLOYMENT**

Aupera's video AI solution provides a full software stack that encompasses video gateway (video decoding/encoding/ streaming & processing), ready to deploy AI models for inference acceleration and a standard API for easy integration with 3rd party software platform. The solution can be deployed on the edge or a regional data center.

\* Note: Multiple cards can be flexibly configured. Current validated servers include: Boston StreamAl server, Dell, Lenovo, Gigabyte, Supermicro. (Specific model information upon request)

The Aupera Smart World solution supports high density video feeds from multiple full HD cameras. The Alveo U30 executes the video decode, scaling and preprocessing and the AMD Alveo™ U50 accelerator runs multiple models needed for Al inference. The number of channels (video streams) and concurrent Al models can be increased by simply adding more AMD Alveo™ accelerator cards.

### LOWER DETERMINISTIC LATENCY

The VMSS framework delivers end-to-end pipeline acceleration by running pre- and post-processing as well as inferencing on the FPGA fabric, delivering deterministic latency about 75% lower than the GPU-based competition in a typical large retailer 32-camera store deployment.

### TAKE THE NEXT STEP

Visit www.xilinx.com/smartworld

#### DISCLAIMERS

The information contained herein is for informational purposes only and is subject to change without notice. While every precaution has been taken in the preparation of this document, it may contain technical inaccuracies, omissions and typographical errors, and AMD is under no obligation to update or otherwise correct this information. Advanced Micro Devices, Inc. makes no representations or warranties with respect to the accuracy or completeness of the contents of this document, and assumes no liability of any kind, including the implied warranties of noninfringement, merchantability or fitness for purposes, with respect to the operation or use of AMD hardware, software or other products described herein. No license, including implied or arising by estoppel, to any intellectual property rights is granted by this document. Terms and limitations applicable to the purchase or use of AMD's products are as set forth in a signed agreement between the parties or in AMD's Standard Terms and Conditions of Sale.

© Copyright 2023 Advanced Micro Devices, Inc. All rights reserved. Xilinx, the Xilinx logo, AMD, the AMD Arrow logo, Alveo, Artix, Kintex, Kria, Spartan, Versal, Vitis, Virtex, Vivado, Zynq, and other designated brands included herein are trademarks of Advanced Micro Devices, Inc. Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies. AMBA, AMBA Designer, ARM, ARM1176JZ-S, CoreSight, Cortex, and PrimeCell are trademarks of ARM in the EU and other countries. PCIe, and PCI Express are trademarks of PCI-SIG and used under license. Printed in the U.S.A. SF 1-21-22